# DESIGN AND SIMULATION OF DIGITALLY CONTROLLED OSCILLATOR OF ADPLL

Sudhakiran Gunda<sup>1</sup>, Dr. Ernest Ravindran R. S.<sup>2</sup>, B. Hemalatha<sup>3</sup>, C. Divya<sup>4</sup> <sup>1</sup>Assistant Professor, <sup>2</sup>Assistant Professor, <sup>3</sup>Student, <sup>4</sup>Student <sup>1, 3, 4</sup>ECE Department, AITS Rajampet, Andhra Pradesh, India – 516115, <sup>2</sup>ECE Department, K L University Campus, Vaddeswaram Village, Andhra Pradesh, India-522502 <sup>1</sup>email id: sudhakiran.495@gmail.com

emaii ia. suanakiran.495@gmaii.com

Abstract: In biomedical implants, the RF transceivers require the low power and less size components for acquiring best results in frequency and phase controlling. The RF transceivers obtain the information from either sides of sources in biomedical applications. Access the signal from human body and processed it through amplifiers, Phase Locked Loops (PLLs), mixers & filters and many more for controlling the parameters. Majorly the PPLs provide the required frequency for the entire operation to obtain this All Digital Phase Locked Loop (ADPLL) is mostly used. In ADPLL, DCO is a major block through which fine frequency resolution is achieved. The present project concentrates on designing the low power Digitally Controlled Oscillator (DCO). Keywords: PLL, ADPLL, DCO, Low Power, Frequency tuning.

#### I.INTRODUCTION

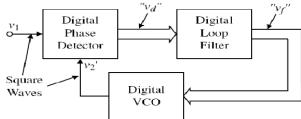

Currently in high performance systems All-Digital Phase Locked Loops (ADPLLs) are used. With the utilization of ADPLLs in digital communication systems, the use of digitally controlled oscillators (DCO) over voltage controlled oscillators (VCO) has come into existence. The general block diagram of ADPLL is shown in figure 1. In general ADPLLs the phase detector generates an output (v<sub>d</sub>) phase/frequency signal by consideration of difference between the input (v<sub>1</sub>) and signals from DCO/Digital VCO (v<sub>2</sub>'). Later "v<sub>d</sub>" undergoes through a filter and responsed as "v<sub>f</sub>" this once again linked with DCO and generated as "v<sub>2</sub>"". This controlled closed loop function will continue till the end of the process. In this scenario DCO has a crucial role.

Fig.1. General block diagram of ADPLL

Hence a low voltage and low power digitally controlled oscillator (DCO) utilized in a medical implant communication service (MICS) frequency band designing is the aim of this paper. In this paper, a new low power DCO structure is proposed with NMOS delay cells as switching network.

### II. DCO

Due to the development of technologies like nano, femto, IOTs the usage of digital components or ADPLLs in various interactive devices proposes the DCO. This paper concentrates on DCOs evolution in modern electronic devices as well as their performances in local oscillators. Research is still continuing on DCOs to get best performance in device area, fastness, range of frequency, power dissipation, low supply voltages etc. The aim is to understand and track the advances in DCO based on its performance level.

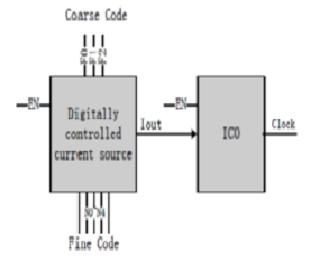

DCO is an oscillator circuit that produces simple flag whose recurrence is constrained by advanced information. Be that as it may, in the event of VCO, recurrence is set by the control voltage. The following diagram shows the basic block diagram of DCO.

The functional block diagram of DCO circuit is shown in Fig. It is composed of current controlled oscillator and digitally controlled current source. F0~F1 is the Coarse Code of tuning output current from the digitally controlled current (DCO) source, while N0~N4 is a Fine Code. The controlled bits F0~F1 and N0~N4 influences the value of output current so as to determine the frequency of the output clock signal from the current controlled oscillator. **2.1 Overview of DCO:**

Digitally Controlled Oscillator (DCO) was planned with the goal that the oscillator is controlled carefully. For the control of recurrence scope of oscillator utilizing an advanced escalated approach, computerized control words in paired bits are bolstered into the oscillator. These

DOI: 10.22413/ijastems/2019/v5/i12/49609

advanced control words are coordinated in a DCO center that controls the recurrence scope of oscillator.

# 2.2 Types of DCO:

The different types of DCOs are:

- 1. Divide by N counter

- 2. Increment/Decrement counter

- 3. Bootstrapped DCO

- 4. XNOR DCO

- 5. LC DCO

a . .

| S.No. | DCO                                 |                                                                                                                                                         |                                                                                                          |  |

|-------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

|       | Types                               | Advantages                                                                                                                                              | Disadvantages                                                                                            |  |

| 1     | Divide by N<br>counter              | Lucid<br>architecture<br>[2]                                                                                                                            | No Jitter design<br>concept [2]                                                                          |  |

| 2     | Increment –<br>Decrement<br>Counter | Mastery over<br>Hold & Lock<br>range [1]                                                                                                                | Software<br>implementation<br>is not possible<br>[1]                                                     |  |

| 3     | Bootstrapped<br>DCO                 | High<br>linearity &<br>resolution [3]                                                                                                                   | Heavy<br>architecture [3]                                                                                |  |

| 4     | XNOR DCO                            | Direct path<br>between<br>VDD and<br>GND is<br>eliminated<br>through<br>optimized<br>XNOR gate.<br>Power<br>Dissipation<br>reduced<br>[present<br>work] | Because of the<br>resistance of<br>switch network<br>the circuit delay<br>is increased<br>[present work] |  |

| 5     | Differential<br>LCDCO               | Good at low<br>voltage<br>operations                                                                                                                    | Introduce noise<br>at high<br>frequency<br>ranges                                                        |  |

# 2.3 Performance of DCO:

The advancement of DCO execution depends on CMOS scaling, supply voltage, goals, control utilization and recurrence tuning range. The execution development for every parameter base on proposed examines is portrayed beneath.

#### 2.3.1 Technology scaling:

Downsizing of CMOS components has been the driving force for DCO evolution. The CMOS technology development has been advanced with the downscaling of component size since the replacement of vacuum tubes with transistors few decades ago. This advanced technology process which leads to deep-sub micrometer CMOS benefits a lot to the circuit characteristics. Now, we are able to integrate millions of CMOS transistors in nano-scale in a silicon chip with few centimetres square. As the technology advances, the latest microprocessor

www.ijastems.org

operates at 3 GHz and is expected to increase further as well as RF communication devices.

#### 2.3.2 Supply voltage in DCO implementation

Supply voltage is the most imperative explanation behind the replacing of VCO with DCO. Supply voltage is the working voltage for any type of oscillator. At the point when the CMOS downscaling was brought into the electronic field, the supply voltage likewise should have been decreased. Decrease of supply voltage in a simple circuit causes breakdown and unwavering quality issues. In this manner, the supply voltage must be little so as to accomplish an elite dimension. ADPLL utilizes the cellbased planned approaches other than LC or RC based, so it very well may be effectively incorporated into the computerized framework.

## 2.4 Power consumption in DCO implementation:

Power utilization of DCO ought to be decreased to spare by and large power dissemination to fulfill low power needs in SoC structures. ADPLL has a noteworthy inconvenience of extensive power utilization and 50 % of all out power is contributed by DCO. Power utilization is critical in convenient battery worked gadgets. Therefore, control sparing has turned out to be significant structure worry in current electronic gadgets. As the time passes, the power utilization has been diminished by improving the circuit plan. Low power prerequisites keep on being requesting for purchaser and different distinctive applications. All DCOs in PLLs being made today require a cost touchy power mindful vitality productive structure that can empower better frameworks. Building up the CMOS innovation and configuration to help exceptionally low power tasks is trying because of expanding gadget varieties and irregular changes. Along these lines, we depend on the improvement of innovation, yet need to search for novel circuit procedures and circuit topologies.

#### **III. RESULTS AND DISCUSSION**

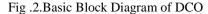

DCO designed in this paper using XNOR based inverter with NMOS delay cells, which were connected in ring topology. Constructed and simulated using Tanner tools in 150nm technology. The operation of the circuit is as follows: the DCO shown in figure 3 with 3 delay cells with 3 control bits consists of a switch network with 4 NMOS transistors. These transistors are binary weighted with the first NMOS gate terminal connected to VDD supply for the provision of current conduction. The control bits  $D_0$ ,  $D_1 \& D_2$  connected to remaining 3 NMOS transistors. The bit requirement decides by the frequency tuning range.

The extension may also possible for the proposed circuit, may implement using either 4 or 6 bit control DCO. But limited to 6-bit DCO due to circuit complexity issues. The control bits in 4-bit DCO ( $D_0$  to  $D_3$ ) and in 6-bit DCO ( $D_0$  to  $D_5$ ) are connect to weighted NMOS transistors.

Volume.5, Issue.3, March. 2019

DOI: 10.22413/ijastems/2019/v5/i12/49609

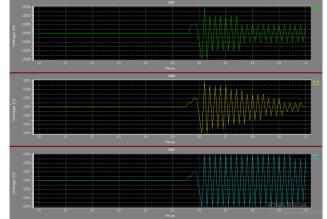

Fig.3.Schematic of DCO The output of the figure 3 is shown as follows:

The graph drawn in between time in nano seconds and voltage in Volts, the first part in the waveform is obtained after the first stage of DCO circuit which provides less range of frequency ranges [1.3 to 1.67 GHZ]. The second obtained after the second stage which gives the moderate frequency range [1.25 to 1.67 GHZ]. The next one is at the output stage of proposed DCO which gives the best range of frequency for bio-medical applications [1 to 1.6 GHZ]. The power consumption for the proposed DCO structure, minimum power consumption is 6.813005e-003W at time 6.2e-007 Sec, the maximum power consumption is 6.817266e-003W at time 6.1e-007 SEC and the average power consumed for all combination of bits in DCO is 6.815116e-003W.

| 1 | abie II. Compa      | 1                             |                            |                     |

|---|---------------------|-------------------------------|----------------------------|---------------------|

|   | DCO<br>architecture | Power<br>dissipation<br>in mW | O/P<br>frequency<br>in GHz | Technolo<br>gy (μm) |

|   | Ref [4]             | 63.4                          | .333-1.47                  | 0.35                |

|   | Ref [5]             | 5.4                           | 0.08-0.25                  | 0.18                |

|   | Ref [6]             | 25                            | 1.2                        | 0.6                 |

| Table II: | Com | parison | with | previous | circuits |  |

|-----------|-----|---------|------|----------|----------|--|

|           |     |         |      |          |          |  |

| Present   | 6.8* | 1.0 -1.6 | 0.15 |

|-----------|------|----------|------|

| work NMOS |      |          |      |

| DCO       |      |          |      |

|           |      |          |      |

#### CONCLUSION

The new structure for DCO using delay cells with control bits have been proposed in the present paper. The resistance nature of the circuit varies with respect to digital control bits and delay has been modulated. Due to an optimized circuit the power consumption of the proposed circuit is reduced noticeable. The DCO provides the output frequency range 1.0 to 1.6 GHZ with a power consumption of 6.8mWatts. The earlier reported details comparison table in terms of power dissipation, frequency ranges and technology used for design also presented in this paper. Based on the comparison table it is proved that the proposed circuit provides wide range of frequency with low power consumption.

#### REFERENCES

[1] R. E. Best, *Phase Locked Loops Design Simulation and Applications*, McGraw-Hill Professional, ch. 6, pp. 205-246, 5th Edition, 2003.

[2] S. Vallabhaneni, et.al Design of an all-Digital PLL core on FPGA.

[3] Yingchieh Ho, et. al "A Near-Threshold 480 MHz 78  $\mu$ W All-Digital with a Bootstrapped DCO ", IEEE Journal of Solid-State Circuits. Vol. 48, No. 11, November 2013.

[4] Tomar A, et al. "Design of 1.1 GHz highly linear digitallycontrolled ring oscillator with wide tuning range". IEEE International Workshop on Radio-Frequency Integration Technology, 2007: 82

[5] Chung Y M, et al. "An all-digital phase-locked loop for digital power management integrated chips". IEEE International Symposium on Circuits and Systems, 2009: 2413

[6] Leung L K, et al. "A giga-hertz CMOS digital controlled oscillator". IEEE International Symposium on Circuits and Systems, 2001, 4: 610

[7] Zhao J,et al. "A low power 32 nanometer CMOS digitally controlled oscillator". IEEE SoC Conference, 2008: 183

[8] Hasan S M R. "A CMOS DCO design using delay programmable differential latches and a novel digital control scheme". Springer Electrr Engg, 2007: 569

[9] Staszewski R B, et al. "A first multi gigahertz digitally controlled oscillator for wireless applications". IEEE Trans Microw Theory Tech, 2003, 51(11): 2154

[10] Kavala A, et. al. "A 5.6 GHz LC digitally controlled oscillator with high frequency resolution using novel quadruple resolution varactor". IEEE International Conference on SoC Design (ISOCC), 2010: 279

[11] Pokharel R K, et al. "Low phase noise 10 bit 5 GHz DCO using on-chip CPW resonator in 0.18nm CMOS technology". IEEE First Asian Himalayas International Conference on Internet, 2009: 1

[12] Staszewski R B, et al. "A digitally controlled oscillator in a 90 nm digital CMOS process for mobile phones". IEEE J Solid-State Circuits, 2005, 40(11): 2203

[13] Shinwoong Kim, Seunghwan Hong, Kapseok Chang, Hyungsik Ju, Jaewook Shin, Byungsub Kim, Hong-June Park and Jae-Yoon Sim, "A 2 GHz Synthesized Fractional-N ADPLL With Dual-Referenced Interpolating TDC", IEEE JOURNAL OF SOLID-STATE CIRCUITS, 0018-9200 © 2015 IEEE

[14] Hamed Abbasizadeh, Imran Ali, Behnam Samadpoor Rikan, Dong-Soo Lee, YoungGun Pu, Sang-Sun Yoo, Minjae Lee, Keum Cheol Hwang, Youngoo Yang, and Kang-Yoon Lee,

DOI: 10.22413/ijastems/2019/v5/i12/49609

"260 uW DCO with Constant Current over PVT Variations using FLL and Adjustable LDO", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, VOL. XX, NO. XX, JANUARY 2018.

[15] Taekwang Jang, Seokhyeon Jeong, Dongsuk Jeon, Kyojin David Choo, Dennis Sylvester and David Blaauw, "A Noise Reconfigurable All-Digital Phase-Locked Loop Using a Switched Capacitor Based Frequency-Locked Loop and a Noise Detector", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 53, NO. 1, JANUARY 2018.

[16] Augusto Ronchini Ximenes, Gerasimos Vlachogiannakis and Robert Bogdan Staszewski, "An Ultracompact 9.4-14.8-GHz Transformer-Based Fractional-N All-Digital PLL in 40-nm CMOS", IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES 0018-9480 © 2017 IEEE.

Sudha Kiran Gunda,, Assistant Professor, AITS Rajampeta born in Bethamcherla, Andhra Pradesh, India in 1989. He received Bachelor Degree in Electronics and Communication Engineering from JNTUA Anantapuramu, India in 2011 and M.Tech Degree in VLSI SD from JNTUA Anantapuramu, India in 2013. He is

currently working towards Ph.D in VLSI domain at K L University, Guntur, A.P. India. His current research interests focus on low power, high performance CMOS digital ICs.

Dr. R. S. Ernest Ravindran received his PhD from Anna University, Chennai, India. He did his Masters in Nanoscience and Technology from Anna University, Trichy, India where he established surface coated CdS quantum dots as a luminescent probe for silver ion detection. His field of research involves Nano Composites (ceramic-polymer) for high energy storage

application, green synthesis of metal nanoparticles in biomedical applications. He is currently working as assistant professor at K L E F(Deemed to be University) Vaddeswaram, Guntur, Andhra Pradesh, India.