International Journal of Advanced Scientific Technologies, Engineering and Management Sciences (IJASTEMS-ISSN: 2454-356X) Volume.3, Special Issue.1, May. 2017

# COMPARATIVE STUDY OF THD REDUCTION FOR ASYMMETRICAL CASCADED H-BRIDGE INVERTER

<sup>1</sup>K.Sripriadarsini, <sup>1</sup>Ph.D, Scholar, Department of Electrical & Electronics Engineering, Dr.M.G.R. Educational & Research Institute University, Chennai, India. darshinisri@gmail.com

<sup>2</sup>Dr.K.Sujath, <sup>2</sup> Professor, Department of Electrical & Electronics Engineering, Dr.M.G.R. Educational & Research Institute University, Chennai, India. drksujatha23@gmail.com

Abstract— This paper proposes the performance of single phase seven, thirteen and twenty seven level asymmetrical cascaded Hbridge multilevel inverter. This proposed inverter widely used in industrial applications such as speed control of induction motor, brushless dc motor etc. This paper reveals the reduction of total harmonic distortion when the number of levels gets increased. FFT analysis and output result of inverter is discussed in this paper.

Index Terms—Asymmetric, Multilevel inverter, THD, Voltage levels.

## **I.INTRODUCTION**

Multilevel inverter is used to convert uncontrolled D.C to controlled A.C. In recent years, asymmetric multilevel inverters have received increasing attention because it is possible to synthesize voltage waveforms with reduced harmonic content, even using a few series- connected cells. In this paper seven, thirteen, twenty seven level inverter with it results has been discussed. For pulse generation sinusoidal pulse width modulation technique is used. This technique is most widely used in industrial application. FFT is used to determine the harmonic analysis for seven, thirteen and twenty seven level inverter.

Multilevel inverters include an array of power semiconductors and dc voltage sources, the output of which generate voltages with stepped waveforms. In comparison with a two-level voltage-source inverter (VSI), the multilevel VSI enables to synthesize output voltages with reduced harmonic distortion and lower electromagnetic interference.

By increasing the number of levels in the multilevel inverters, the output voltages have more steps in generating a staircase waveform, which has a reduced harmonic distortion.

#### II. PROPOSED SYSTEM

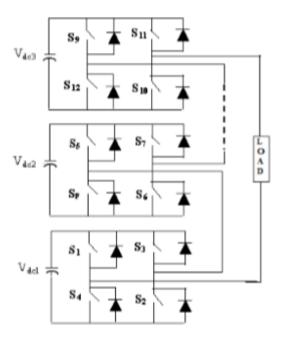

Multilevel inverter owns a separate DC source to form a single phase full bridge or H-bridge inverter. By different combination of four switches S1, S2, S3 and S4, it can generate the three different output voltage +Vdc, 0, -Vdc.

The switches S1 and S4 turned on to obtain a +Vdc, for -Vdc the switches S2 and S3 gets turn on. The output voltage is 0 when the switches S1 and S4 or S2 and S3 are turn on. Here, the final output voltage levels becomes the sum of each terminal voltage of H-bridge, and it is given as

$$\mathbf{V}_{\text{out}} = \mathbf{V}_{\text{HB1}} + \mathbf{V}_{\text{HB2}} \tag{1}$$

Figure 1: General Circuit for H-Bridge Inverter

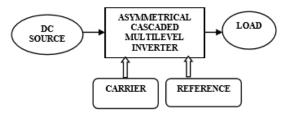

Figure 2: Block Diagram of Proposed syste

III. CIRCUIT DIAGRAM OF PROPOSED SYSTEM

### International Conference on Advances In Computing ,Electrical and Communication Engineering(ICACECE-2017)

International Journal of Advanced Scientific Technologies, Engineering and Management Sciences (IJASTEMS-ISSN: 2454-356X) Volume.3, Special Issue.1, May. 2017

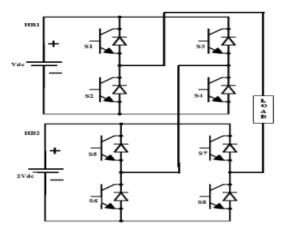

Circuit diagram of Asymmetrical H-bridge multilevel inverter employing Binary DC input source shown in figure 3. By using Vdc, 2Vdc. it can synthesize seven output levels; 0, Vdc, 2Vdc, 3Vdc, -Vdc, -2Vdc, -3Vdc.

In the proposed circuit topology, if n is number of Hbridge module has independent DC sources in sequence of the power of 2 an expected output voltage level is given as  $Vn = 2^n$ , n = 1,2,3 (4)

Figure 3: Circuit Diagram for Seven Level Inverter

Figure 4: Circuit Diagram for Thirteen Level Inverter

Figure 4 shows the thirteen level inverter. It can synthesis fifteen output level 0, Vdc ,2Vdc , 3Vdc , 4Vdc , 5Vdc , 6Vdc , -Vdc , -2Vdc , -3Vdc , -4Vdc , -5Vdc ,6Vdc.

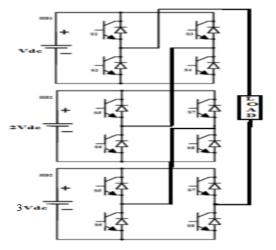

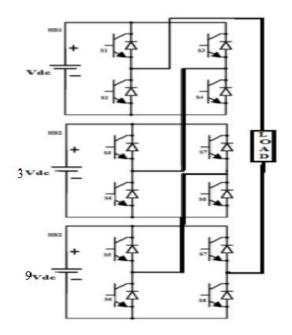

Figure 5: Circuit Diagram for Twenty Seven Level Inverter

Fig 5 shows the circuit diagram of twenty seven level inverter which is similar to the thirteen level circuit only difference is the value of dc voltages applied to each bridge. The ratio is 1:3:9 for twenty seven level inverter.

#### VI. SIMULATION RESULTS

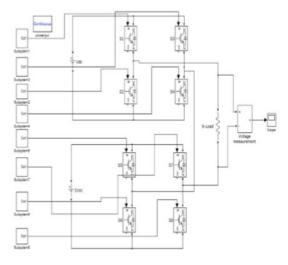

The simulation model is done by using MATLAB / SIMULINK. The analyses of total harmonic distortion for proposed systems are given below:

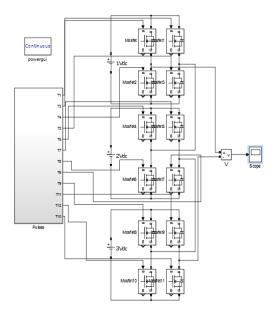

Figure 6: Simulation Circuit for Seven Level Inverter

## International Conference on Advances In Computing ,Electrical and Communication Engineering(ICACECE-2017)

International Journal of Advanced Scientific Technologies, Engineering and Management Sciences (IJASTEMS-ISSN: 2454-356X) Volume.3, Special Issue.1, May. 2017

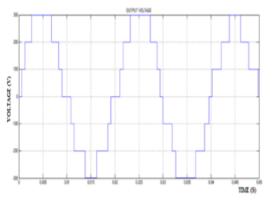

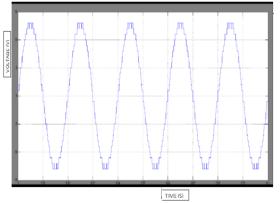

Figure 7: Output Voltage Waveform for Seven Level Inverter

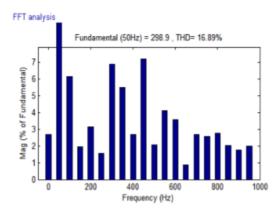

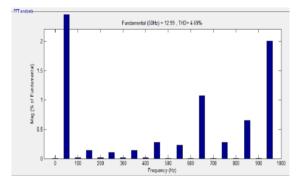

Figure 8: FFT for Seven Level Inverter

The figures 6,7 and 8 shows the simulation diagram, output voltage waveform and the FFT analysis for seven level inverter and the THD is obtained as 16.89%.

Figure 9: Simulation Circuit of Thirteen Level Inverter

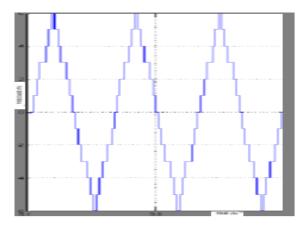

Figure 10: Output Voltage Waveform for Thirteen Level Inverter

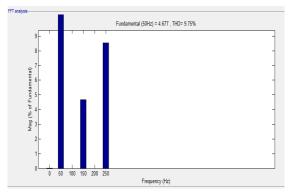

Figure 11: FFT for Thirteen Level Inverter

The figures 9,10 and 11 shows the simulation diagram, output voltage waveform and the FFT analysis for thirteen level inverter and the THD is obtained as 9.75%.

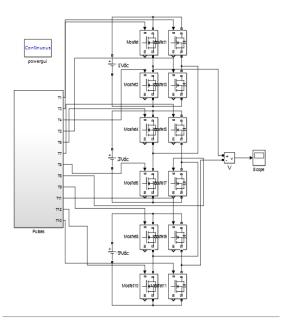

Figure 12:Simulation Circuit of Twenty Seven Level Inverter.

## International Conference on Advances In Computing ,Electrical and Communication Engineering(ICACECE-2017)

International Journal of Advanced Scientific Technologies, Engineering and Management Sciences (IJASTEMS-ISSN: 2454-356X) Volume.3, Special Issue.1, May. 2017

Figure 13:Output Voltage Waveform of Twenty Seven Level Inverter.

Figure 14:FFT analysis of Twenty Seven Level Inverter

Figures 12,13 and 14 level inverter shows the simulation diagram, output voltage waveform and FFT analysis for twenty seven level inverter and the THD is 4.69%.

| V.COMPARATIVE | ANALYSIS |

|---------------|----------|

|---------------|----------|

| S.NO | NO OF LEVELS | THD    |

|------|--------------|--------|

| 1.   | 7 LEVEL      | 16.89% |

| 2.   | 13 LEVEL     | 9.75%  |

| 3.   | 27 LEVEL     | 4.69%  |

| Table 1 | : | Comparative | Ana | lysis |

|---------|---|-------------|-----|-------|

|---------|---|-------------|-----|-------|

From above comparative analysis, we can note that twenty seven level inverter has low total harmonic distortion compare to seven and thirteen level.

## V. CONCLUSION

In proposed work, the performance of asymmetrical cascaded H-bridge seven level, thirteen level and twenty seven level inverter has been analysed by MATLAB / SIMULINK. From above comparative table, the twenty seven level inverter has **4.69%**, which has low total harmonic distortion compared to seven level and thirteen level inverter.

#### REFERENCES

- M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Peréz, "A survey on cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197–2206, Jul. 2010.

- [2] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-pointclamped PWM inverter," IEEE Trans. Ind. Electron., vol. IA-17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [3] J. S. lai and F. Z. Peng, "Multilevel converters-a new breed of power converters," IEEE Trans. Ind. Appl., vol. 32, no. 3, pp. 509–517, May/ Jun. 1996. [4] P. Hammond, "A new approach to enhance power quality for medium voltage AC drives," IEEE Trans. Ind. Electron., vol. 33, no. 1, pp. 202– 208, Jan./Feb. 1997.

- [5] E. Cengelci, S. U. Sulistijo, B. O. Woo, P. Enjeti, R. Teodorescu, and F. Blaabjerg, "A new medium-voltage PWM inverter topology for adjustable-speed drives," IEEE Trans. Ind. Appl., vol. 35, no. 3, pp. 628–637, May/Jun. 1999.

- [6] J. Rodriguez, L. G. Franquelo, S. Kouro, J. I. Leon, R. C. Portillo, M. A. M. Prats, and M. A. Perez, "Multilevel converters: An enabling technology for high-power applications," Proc. IEEE, vol. 97, no. 11, pp. 1786–1817, Nov. 2009. [7] O. M. Mueller and J. N. Park, "Quasi-linear IGBT inverter topologies," in Proc. IEEE APEC, Orlando, FL, USA, Feb. 13–17, 1994, pp. 253–259. [8] I. Colak, R. Bayindir, and E. Kabalci, "Design and analysis of a 7-level cascaded multilevel inverter with dual SDCs," in Proc. Int. SPEEDAM, Pisa, Italy, Jun. 14–16, 2010, vol. 1, pp. 180–185. [9] S. Mariethoz and A. Rufer, "Design and control of asymmetrical multilevel inverters," in Proc. IEEE IECON, Seville, Spain, Nov. 5–8, 2002, pp. 805–845.

- [10] M. N. A. Abdul, Kadir, and Z. F. Hussein, "Asymmetrical multilevel inverter: Maximum resolution for H-bridge topology," in Proc. Int. Conf. PEDS, Kuala Lumpur, Malaysia, Nov./Dec. 2005, vol. 2, pp. 1068–1071.

- [11] M. Perez, J. Rodriguez, J. Pontt, and S. Kouro, "Power distribution in hybrid multi-cell converter with nearest level modulation," in Proc. IEEE ISIE, Vigo, Spain, Jun. 4–7, 2007, pp. 736–741.

- [12]S.Kouro, M.Malinowski, K.Gopakumar, J.Pou, L.G.Franquelo, B.Wu,J.Rodriguez, M.A.Perez and J.I.Leon, "Recentadvancesandindustrial applications of multilevel converters, "IEEETrans. Ind. Electron., vol.57, no. 8, pp. 2553–2580, Aug. 2010.