# NEW CONCEPT OF MULTILEVEL INVERTER TOPOLOGY

## SHAIK IQLAB<sup>1</sup>, T. VEERENDRA<sup>2</sup>

## <sup>1</sup>M.Tech (P.E)scholar Dept of EEE,ANURAG College of Engineering <sup>2</sup>Assisant Professor, Dept of EEE, ANURAG College of Engineering

Abstract— Multi level inverters have been widely accepted for high-power high-voltage applications. Their performance is highly superior to that of conventional Seven-level inverters due to reduced harmonic distortion, lower electromagnetic interference, and higher dc link voltages. In this paper, a new topology with a reversing-voltage component is proposed to improve the multilevel performance. This topology requires fewer components compared to existing inverters (particularly in higher levels) and requires fewer carrier signals and gate drives. Therefore, the complexity is greatly reduced particularly for higher output voltage levels. The Proposed 15-level inverter is modelled and simulated in Matlab 2012a using Simulink and Sim Power Systems set tool boxes.

Index Terms—: Multilevel inverter, power electronics, SPWM, topology

#### I. INTRODUCTION :

Advancement in the research of Power electronic inverters is still increasing with the rapid demands in electrical systems. The emergence of multilevel inverters has been in increase since the last decade. These new types of converters are suitable for high voltage and high power application due to their ability to synthesize waveforms with better harmonic spectrum[10].

Multilevel converters are mainly utilized to synthesis a desired single- or three-phase voltage waveform. The desired multi-staircase output voltage is obtained by combining several dc voltage sources. Solar cells, fuel cells, batteries and ultra-capacitors are the most common independent sources used [1]. One important application of multilevel converters is focused on medium and high-power conversion. Nowadays, there exist three commercial topologies of multilevel voltage-source inverters: neutral point clamped (NPC), cascaded H-bridge (CHB), and flying capacitors (FCs)[2]. Among these inverter topologies, cascaded multilevel inverter reaches the higher output voltage and power levels (13.8 kV,30 MVA) and the higher reliability due to its modular topology[3].

Diode-clamped multilevel converters are used in conventional high-power ac motor drive applications like conveyors, pumps, fans, and mills. They are also utilized in oil, gas, metals, power, mining, water, marine, and chemical industries. They have also been reported to be used in a back-to-back configuration for regenerative applications[4]. Flying capacitor multilevel converters have been used in high-bandwidth high-switching frequency applications such as medium-voltage traction drives. Finally, cascaded H-bridge multilevel converters have been applied where high power and power quality are essential, for example, static synchronous active filter compensators and reactive power compensation applications, photovoltaic power conversion, uninterruptible power supplies, and magnetic resonance imaging. Furthermore, one of the growing applications for multilevel motor drives is electric and hybrid power trains.

For increasing voltage levels the number of switches also will increase in number. Hence the voltage stresses and switching losses will increase and the circuit will become complex. By using the proposed topology number of switches will reduce significantly and hence the efficiency will improve.

multi-stage Α inverter using three-state converters is being analyzed for multipurpose applications, such as active power filters, static var compensators and machine drives for sinusoidal and trapezoidal current applications. The great advantage of this kind of converter is the minimum harmonic distortion obtained.

The circuit of Fig.1 shows the basic topology of one converter used for the implementation of multi-stage converters. It is based on the simple, four switches converter ,used for single phase inverters or for dual converters. These converters are able to produce three levels of voltage in the load: +Vdc, -Vdc, and Zero[7].

# Fig.1. Basic idea diagram of three-level module for building multi stage inverter

This paper mainly focuses on the general multilevel inverter schematic. A general method of multilevel modulation phase disposition (PD) SPWM is utilized to drive the inverter and can be extended to any number of voltage levels. Here, in this paper the proposed multilevel scheme extended up to 15-levels.. In this work, the asymmetric 15 level inverter is presented. This inverter is designed to avoid the regeneration problem - power flow from the load to the inverter - in some of the power cells. This is achieved by obtaining the firing angles associated with the power cells considering a minimum load voltage THD. The simulation and experimental results of the proposed 15-level inverter topology are also presented. Finally, a power flow analysis is accomplished and simulated results show the feasibility of this approach

#### II. PROPOSED 15-LEVEL INVERTER

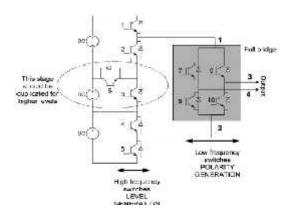

Multilevel inverters are the alternative for medium voltage applications. Within the inverters types there are symmetric and asymmetric topologies. The asymmetric inverters have different DC voltage values. The most common topology is when the different cells are implemented in cascade arrangement, where the DC voltage are in multiples of 3, obtaining an AC voltage with  $3^n = 27$  levels (n = 3 cascaded inverters). This topology provides a load voltage with low harmonic content, THD <; 3%. However, this high quality voltage has a non-negligible drawback, which is the presence of regeneration in some of the inverters, independent of load type[1]. This phenomenon is due to the modulation technique (Nearest Level Modulation) used by this inverter. In this work, the asymmetric 15 level inverter is presented. This inverter is designed to avoid the regeneration problem - power flow from the load to the inverter - in some of the power cells. This is achieved by obtaining the firing angles associated with the power cells considering a minimum load voltage THD. Finally, a power flow analysis is accomplished and simulated results show the feasibility of this approach.Fig.2 shows the proposed inverter fed to 3-phase a.c load and Fig.3 shows the simplified diagram with three inverters per phase.

Fig.2. Basic idea diagram of three-phase inverter

Fig.3. Schematic of seven level inverter in single phase

The most commonly used multilevel topology is the diode clamped inverter, in which the diode is used as the clamping device to clamp the dc bus voltage so as to achieve steps in the output voltage.A three-level diode clamped inverter consists of two pairs of switches and two diodes. Each switch pairs works in complimentary mode and the diodes used to provide access to mid-point voltage. In a three-level inverter each of the three phases of the inverter shares a common dc bus, which has been subdivided by two capacitors into three levels. The DC bus voltage is split into three voltage levels by using two series connections of DC capacitors, C1 and C2. The voltage stress across each switching device is limited to Vdc through the clamping diodes Dc1 andDc2. It is assumed that the total dc link voltage is Vdc and mid point is regulated at half of the dc link voltage, the voltage across each capacitor is Vdc/2(Vc1=Vc2=Vdc/2).[1].

#### A. Switching Sequences:

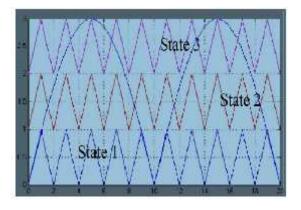

In order to avoid unwanted voltage levels during switching cycles, the switching modes should be selected so that the switching transitions become minimal during each mode transfer. This will also help to decrease switching power dissipation .In order to produce 15levels by Sinusoidal Pulse Width Modulation (SPWM), three saw-tooth waveforms for carrier and a sinusoidal reference signal for modulator are required as shown in Fig. 4.

#### www.ijastems.org

Fig. 4.SPWM carrier and modulator for proposed 15-level inverter

#### III. MATLABBASEDSIMULATION&RESULTS

#### A. MATLAB based simulation :

Fig.4. shows the complete MATLAB based simulation masked diagram of the proposed 15-level, 3-phase

Fig.4.MATLAB based simulation masked diagram of the proposed 15-level, 3-phase inverterFig.5. shows the input DC voltage source to the proposed 15-level, 3-phase inverter

Fig.5. Input DC voltage source to the proposed 15-level, 3-phase inverter

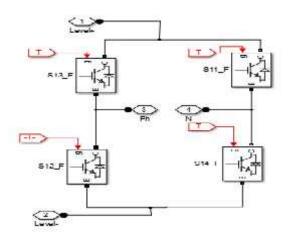

Fig.6. shows power electronic based bridge circuit of the proposed 15-level, 3-phase inverter

Fig.6. Simulation diagram of power electronic based bridge circuit of the proposed 15-level, 3-phase inverter

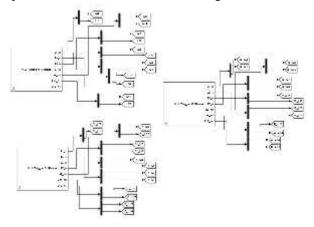

Fig.7. shows the gate controlled pulse to the proposed 15level, 3-phase inverter.Fig.8.shows the inversion of DC to 3-phase MATLAB based simulation diagram.

Fig.8. DC to AC 3-phase inversion MATLAB based simulation diagram.

Simulation parameters for the proposed 15-level, 3-phase inverter is given by in the Table.1

#### B. Simulation Results:

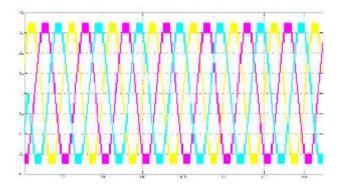

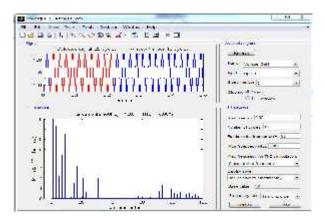

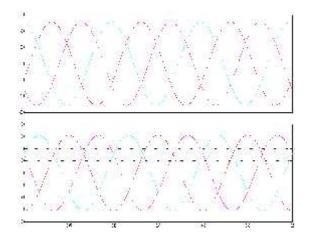

Fig.9.shows the 3-phase, 15-level output voltage waveform from the proposed inverter.Fig.10. shows the THD calculation of proposed 3-phase, 15-level inverter using powergui FFT Analysis tool.

Fig.9. 3-Phase, 15-level output voltage waveform from the proposed inverter

Fig.10. THD calculation of proposed 3-phase, 15-level inverter using powergui FFT Analysis tool

Fig.11. shows the 3-phase voltage and 3-phase current waveform from the proposed inverter.

Fig.11. 3-phase voltage (upper) and 3-phase current (lower) waveform from the proposed inverter respectively

Table .2. Shows the r.m.s values from phase voltages and

currents

#### TABLE1.SIMULATION SPECIFICATIONS

| Parameter                   | Rating |

|-----------------------------|--------|

| Input DC supply (V)         | 50V    |

| IGBT/Diode Internal         | 1 m    |

| Resistance Ron              |        |

| Snubber Resistance , Rs ( ) | 1μ     |

| Nominal frequency (Hz)      | 50 Hz  |

| Active Power (W)            | 10KW   |

| Reactive Power (Var)        | 8Kvar  |

| Damping factor of filter    | 0.8    |

#### TABLE.2. RMS VALUES OF OUTPUT RESPONSES

| Output Response     | RMS Value |

|---------------------|-----------|

| Phase A voltage (V) | 363.4     |

| Phase B voltage (V) | 363.3     |

| Phase C voltage (V) | 363.3     |

| Phase A Current (A) | 43.89     |

| Phase B Current (A) | 43.85     |

| Phase C Current (A) | 43.85     |

#### OF PROPOSED INVERTER

#### **IV.CONCLUSION**

An efficient 3-phase, 15-level inverter is presented in the paper. The resultant simulation graphs show the accuracy of the proposed inverter. High performance switches are adopted to reduce the conduction losses and improve the efficiency. Experimental results that confirm the feasibility of the proposed 3-phase, 15-level inverter. Finally, MATLAB based simulink results showns the THD value at reasonable level.

#### REFERENCES

- [1] K. Gopakumar, Haitham Abu-Rub, P. P. Rajeevan and K.Sivakumar, "A Nine-Level Inverter Topology for Medium-Voltage Induction Motor Drive With Open-End Stator Winding" IEEE Transactions, 2013 on industrial electronics,vol.60, no.9.

- [2] M. N. Abdul Kadir and S. Mekhilef "Novel vector controlmethod for three-stage hybrid cascaded multilevel inverter" IEEE 2011, Trans. Ind.Electron., vol. 58,

- [3] L. A. Córdova, L. Empringham, P. Lezana and C. A. Silva"Implementation and control of a hybrid multilevel converter withfloating dc links for current waveform improvement" IEEE Trans. Ind.Electron., 2011 vol. 58,no. 6.

- [4] Ehsan Najafi and Abdul Halim Mohamed Yatim, "Design and Implementation of a New MultilevelInverter Topology", IEEETrans. Ind. Electron. November 2012, Vol. 59,no. 7, pp.no. 4148-4154

- [5] L. G. Franquelo, K. Gopakumar, S. Kouro, J. I. Leon, M.Malinowski, M. A. Pérez, J. Pou and B.Wu, J. Rodríguez, "Recent advances and industrial applications of multilevel converters" IEEE Trans. Ind. Electron, 2010, vol. 57, no. 8.

- [6] G. Franquelo, S. Kouro, J. I. Leon, R. Portillo, M. A. M.Prats and J. Rodriguez. (2008) "The age of multilevel converters arrives" IEEE 2008, Vol.2, no.2.

- [7] E.Vellaneava ,P.Correa , M.Pacas , "Control of Single-Phase Cascaded H-Bridge Multilevel Inverter for Grid-Connected photovoltaic Systems", IEEE trans. Industrial Eleectronics , 2009 , Vol.56,pp.4399-4406.

- [8] Malinowski Mariusz, Gopakumar K, Rodriguez Jose, Pérez Marcelo A, "A survey on cascaded multilevel inverters", IEEE Trans Ind Electron 2010;57(7).

- [9] Malinowski Mariusz, GopakumarK, Rodriguez Jose, Pérez Marcelo A., "A survey on cascaded multilevel inverters.", IEEE Trans Ind Electron 2010;57(7). Convers Manage 2011;52:1114–28.

- [10] K. Jang-Hwan, S.-K. Sul, and P. N. Enjeti, "A carrierbased PWMmethod with optimal switching sequence for a multilevel four-leg voltage source inverters",*IEEE Trans. Ind. Appl.*, vol. 44, no. 4, pp. 1239–1248, Jul./Aug. 2008.